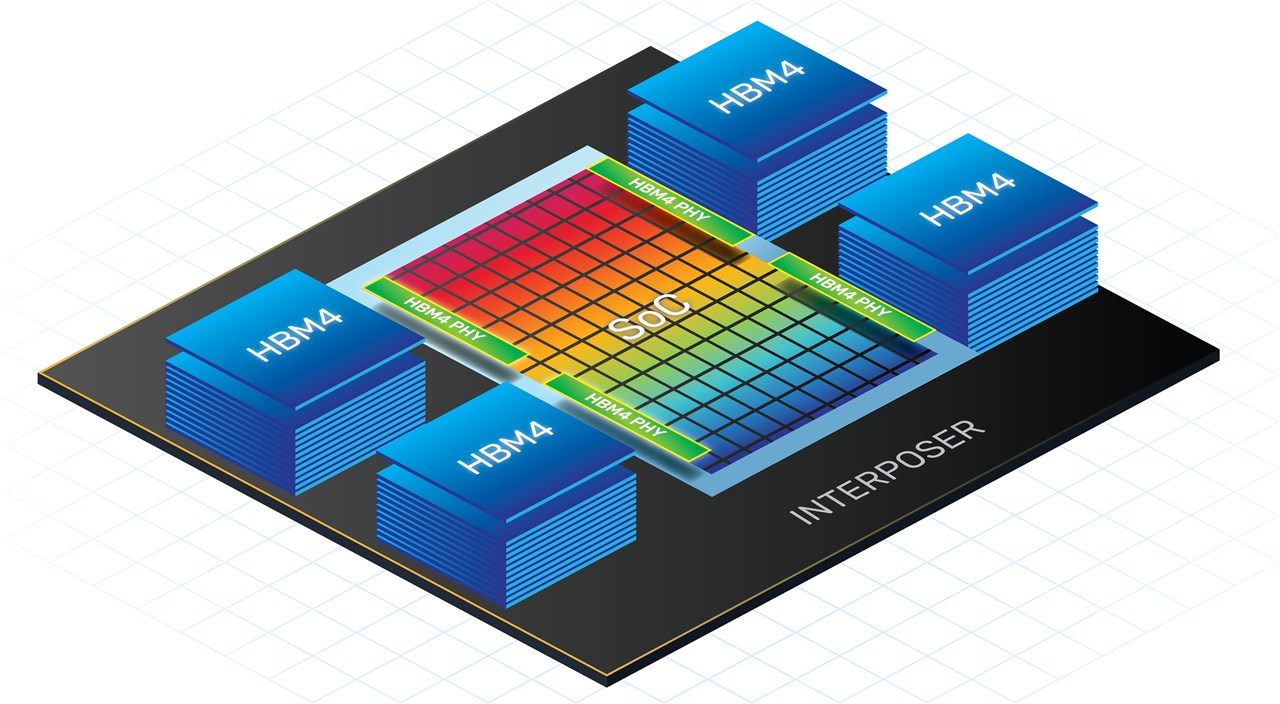

With the dawn of High Bandwidth Memory 4 (HBM4), the memory landscape is set to transform remarkably. This new standard, officially released by JEDEC under the code JESD238, is tailored to meet the escalating demands of artificial intelligence (AI), high-performance computing (HPC), and the sophisticated infrastructure of modern data centers.

HBM4 retains the signature vertical stacked DRAM architecture of its predecessors but introduces significant enhancements in performance. It supports data transfer speeds of up to 8 Gb/s via a robust 2048-bit interface. This configuration allows for a staggering 2 terabytes per second of total bandwidth. A major leap in design is the expansion in the number of independent channels per memory stack, doubling from 16 in HBM3 to 32 in HBM4. Each channel is further divided into two logical pseudo-channels, enhancing parallel processing capabilities and providing increased flexibility in memory access.

HBM4 offers flexibility in its operation at varied voltage levels, catering to different manufacturer preferences, thereby optimizing energy efficiency. Another critical advantage is its backward compatibility, allowing it to function seamlessly with existing HBM3 controllers.

The new standard sets a new benchmark in memory density, supporting DRAM stacks ranging from 4 to 16 and densities from 24Gb to 32Gb. This allows a single HBM4 module to achieve a capacity of up to 64GB with a 16-stack structure of 32Gb, a boon for AI and HPC applications that handle substantial data sets.

Alongside HBM4, JEDEC introduces Directed Refresh Management (DRFM), a system designed to bolster reliability, accessibility, and maintainability. DRFM offers enhanced protection against vulnerabilities like the ‘row hammer’ effect.

The separation of command and data paths in HBM4 reduces latency and increases concurrency in multi-channel operations. Enhanced signal integrity and a new physical interface facilitate consistent achievement of higher data rates.

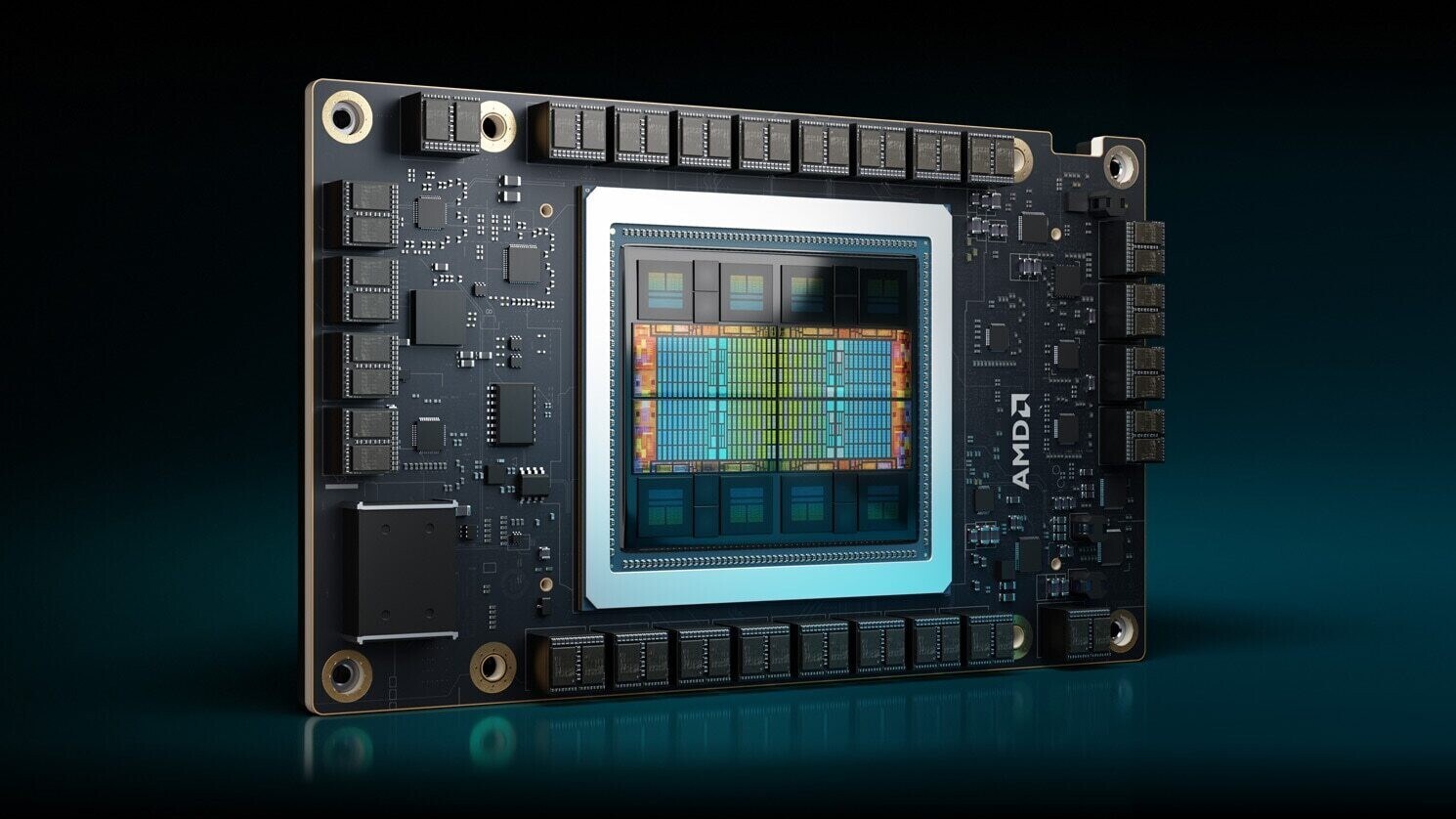

Leading industry players such as Samsung, Micron, and SK Hynix have been instrumental in developing the HBM4 standard. These companies are poised to release HBM4-compatible products by 2025. The anticipation is growing, especially among AI chip manufacturers and hyperscale data centers eager to harness the advanced capabilities of HBM4.

ENGLİSH

5 gün önceSİGORTA

5 gün önceSİGORTA

5 gün önceSİGORTA

8 gün önceSİGORTA

10 gün önceSİGORTA

10 gün önceDÜNYA

19 gün önce 1

Elon Musk’s Father: “Admiring Putin is Only Natural”

11559 kez okundu

1

Elon Musk’s Father: “Admiring Putin is Only Natural”

11559 kez okundu

2

xAI’s Grok Chatbot Introduces Memory Feature to Rival ChatGPT and Google Gemini

10584 kez okundu

2

xAI’s Grok Chatbot Introduces Memory Feature to Rival ChatGPT and Google Gemini

10584 kez okundu

3

Minnesota’s Proposed Lifeline Auto Insurance Program

9475 kez okundu

3

Minnesota’s Proposed Lifeline Auto Insurance Program

9475 kez okundu

4

Introducing Vivo Y300 Pro+: A Blend of Power and Affordability

7413 kez okundu

4

Introducing Vivo Y300 Pro+: A Blend of Power and Affordability

7413 kez okundu

5

What’s the best car insurance for seniors?

6070 kez okundu

5

What’s the best car insurance for seniors?

6070 kez okundu

Veri politikasındaki amaçlarla sınırlı ve mevzuata uygun şekilde çerez konumlandırmaktayız. Detaylar için veri politikamızı inceleyebilirsiniz.