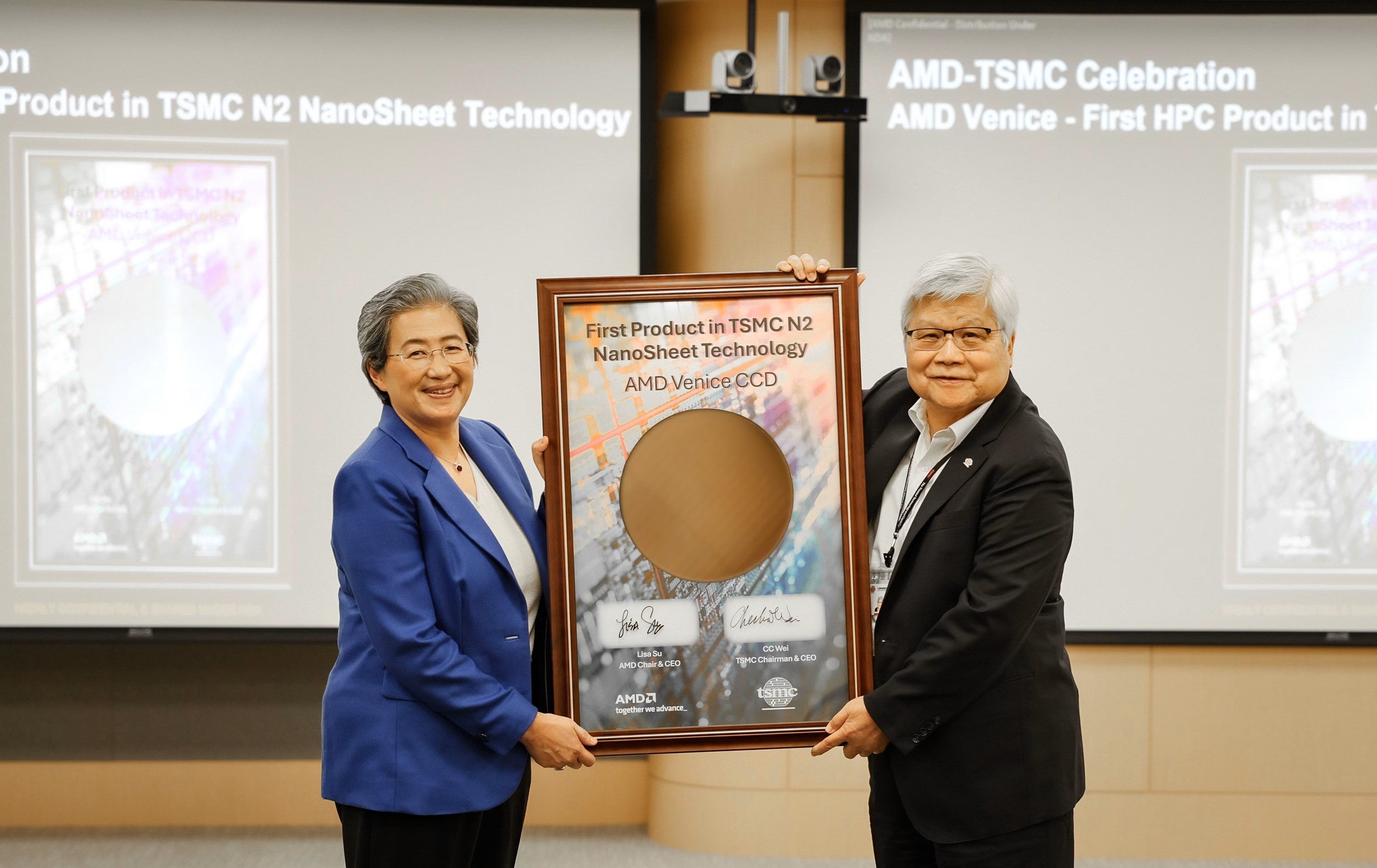

AMD has unveiled a transformative development in the data center sector with its announcement of the next generation of EPYC processors. Codenamed “Venice” and incorporating the advanced Zen 6 architecture, these processors are set to redefine high-performance computing (HPC) with their production on TSMC‘s cutting-edge N2 (2nm) technology—currently the pinnacle of semiconductor manufacturing.

Official details reveal that AMD’s 6th generation EPYC Venice processors will undergo mass production using TSMC’s groundbreaking 2nm (N2) node, which leverages NanoSheet technology. This process is anticipated to deliver substantial enhancements in both processing speed and energy efficiency. The Zen 6 and Zen 6C architectures will harness these advancements to optimize computational power while maintaining energy-conscious operations. The processors will be compatible with the SP7 socket and support either 12 or 16 channels of DDR5 memory.

In a significant stride towards bolstering U.S. semiconductor manufacturing, AMD has also highlighted the successful verification and readiness for production of its 5th generation EPYC processors at Fab 21, TSMC’s state-of-the-art manufacturing facility in Arizona, USA. This milestone aligns with U.S. initiatives to increase domestic semiconductor production—a strategic move to attract such capabilities to American soil. Following in the footsteps of Nvidia, AMD stands as a key client of TSMC’s Arizona plant, marking its commitment to fostering local manufacturing capabilities.

ENGLİSH

4 gün önceSİGORTA

4 gün önceSİGORTA

4 gün önceSİGORTA

8 gün önceSİGORTA

9 gün önceSİGORTA

9 gün önceDÜNYA

18 gün önce 1

Elon Musk’s Father: “Admiring Putin is Only Natural”

11536 kez okundu

1

Elon Musk’s Father: “Admiring Putin is Only Natural”

11536 kez okundu

2

xAI’s Grok Chatbot Introduces Memory Feature to Rival ChatGPT and Google Gemini

10522 kez okundu

2

xAI’s Grok Chatbot Introduces Memory Feature to Rival ChatGPT and Google Gemini

10522 kez okundu

3

Minnesota’s Proposed Lifeline Auto Insurance Program

9458 kez okundu

3

Minnesota’s Proposed Lifeline Auto Insurance Program

9458 kez okundu

4

Introducing Vivo Y300 Pro+: A Blend of Power and Affordability

7398 kez okundu

4

Introducing Vivo Y300 Pro+: A Blend of Power and Affordability

7398 kez okundu

5

What’s the best car insurance for seniors?

6055 kez okundu

5

What’s the best car insurance for seniors?

6055 kez okundu

Veri politikasındaki amaçlarla sınırlı ve mevzuata uygun şekilde çerez konumlandırmaktayız. Detaylar için veri politikamızı inceleyebilirsiniz.