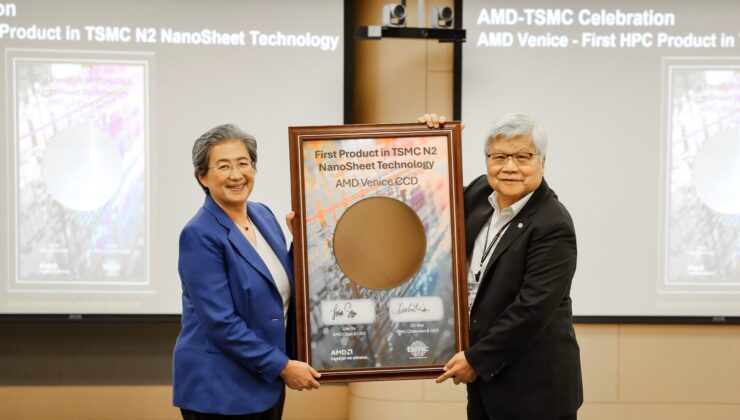

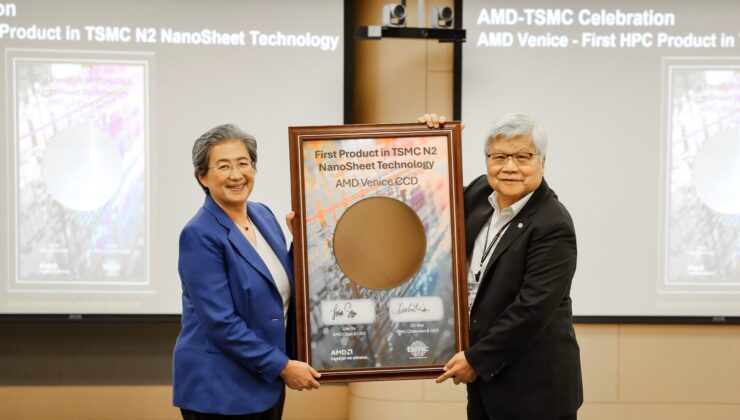

In a significant move, AMD has unveiled a long-term collaboration with TSMC, marking a pivotal moment in the semiconductor industry. This partnership will see the production of AMD’s forthcoming EPYC Venice Zen 6 processors, which are set to be the first high-performance computing products leveraging TSMC’s innovative 2nm N2 manufacturing process. These processors are finely tuned with the new Zen 6 and Zen 6C architectures and incorporate TSMC’s revolutionary NanoSheet technology.

The eagerly anticipated 6th generation EPYC processors, codenamed Venice, are slated for launch next year. This announcement coincides with AMD’s confirmation that the 5th generation EPYC processors have been successfully produced and verified at TSMC’s advanced Fab 21 facility located in Arizona, underscoring a major stride in the United States’ aspirations for domestic chip manufacturing.

“TSMC has been a cornerstone partner for numerous years, and our extensive collaboration with their R&D and manufacturing teams has empowered us to deliver cutting-edge products that redefine the limits of high-performance computing,” stated Dr. Lisa Su, Chairman and CEO of AMD. Echoing this sentiment, Dr. C.C. Wei, TSMC’s Chairman and CEO, remarked, “We are honored to have AMD as a leading high-performance computing customer for our 2nm technology and Arizona fab. Together, we are achieving superior performance, power efficiency, and manufacturing yields for high-performance silicon.”

The Venice processors are designed to utilize the SP7 socket and will support either 12 or 16 channels of DDR5 memory. These advancements signify a crucial leap in AMD’s data center processor roadmap, illustrating the transformative impact of the AMD-TSMC alliance on future computing innovations.

ENGLİSH

5 gün önceSİGORTA

5 gün önceSİGORTA

5 gün önceSİGORTA

8 gün önceSİGORTA

10 gün önceSİGORTA

10 gün önceDÜNYA

19 gün önce 1

Elon Musk’s Father: “Admiring Putin is Only Natural”

11568 kez okundu

1

Elon Musk’s Father: “Admiring Putin is Only Natural”

11568 kez okundu

2

xAI’s Grok Chatbot Introduces Memory Feature to Rival ChatGPT and Google Gemini

10610 kez okundu

2

xAI’s Grok Chatbot Introduces Memory Feature to Rival ChatGPT and Google Gemini

10610 kez okundu

3

Minnesota’s Proposed Lifeline Auto Insurance Program

9484 kez okundu

3

Minnesota’s Proposed Lifeline Auto Insurance Program

9484 kez okundu

4

Introducing Vivo Y300 Pro+: A Blend of Power and Affordability

7421 kez okundu

4

Introducing Vivo Y300 Pro+: A Blend of Power and Affordability

7421 kez okundu

5

What’s New in iOS 19: Updates and Compatibility

6185 kez okundu

5

What’s New in iOS 19: Updates and Compatibility

6185 kez okundu

Veri politikasındaki amaçlarla sınırlı ve mevzuata uygun şekilde çerez konumlandırmaktayız. Detaylar için veri politikamızı inceleyebilirsiniz.